最新文章

XILINX FPGA與DDR2存儲(chǔ)器接口

?DDR2(Double DataRate2)SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會(huì))制定的新生代內(nèi)存技術(shù)標(biāo)準(zhǔn),它與上一代DDR內(nèi)存技術(shù)標(biāo)準(zhǔn)最大的不同:雖然采用 時(shí)鐘的上升/下降沿同時(shí)傳輸數(shù)據(jù)的基本方式,但DDR2卻擁有2倍的DDR預(yù)讀取能力(即4位預(yù)存取技術(shù))。此外,DDR2還增加ODT(內(nèi)建核心終結(jié)電 阻器)功能,內(nèi)建合適的端接電阻,避免了以往因片外連接大片終結(jié)電阻帶來(lái)的制板成本增加。

基 于FPGA的SDRAM控制器,以高可靠性、強(qiáng) 可移植性、易于集成的特點(diǎn),逐漸取代以往的專用控制器而成為主流解決方案。本文采用Xilinx公司的Spartan-3A系列FPGA和Hynix公司 的DDR2 SDRAM器件HY5PS121621實(shí)現(xiàn)DDR2控制器的設(shè)計(jì)。

2 FPGA與DDR2存儲(chǔ)器接口

圖 1所示為 DDR2與FPGA的外圍接口連接圖,DDR2的信號(hào)線分為:時(shí)鐘信號(hào)線CK/CK;數(shù)據(jù)信號(hào)線Data/DQS/DM;地址信號(hào)線 Address/BA1/BA0;命令信號(hào)線RAS/CAS/WE;控制信號(hào)線CS/CKE/ODT。FPGA除與DDR2的所有信號(hào)線相連外,還引出外 部環(huán)回信號(hào)線(圖中虛線所示),此信號(hào)輸出送至輸入輸出模塊(IOB),以補(bǔ)償FPGA與存儲(chǔ)器之間的IOB、器件和跡線的延遲。

差

分時(shí)鐘線CK/CK為DDR2數(shù)據(jù)傳輸提供時(shí)鐘,在CK的上升沿和下降沿均有數(shù)據(jù)被觸發(fā);雙向差分線DQS/DQS看作數(shù)據(jù)的同步信號(hào),寫入時(shí)由控制器發(fā)

出,讀取時(shí)由DDR2產(chǎn)生DQS向控制器發(fā)送,它與讀數(shù)據(jù)邊沿對(duì)齊而與寫數(shù)據(jù)中心對(duì)齊。DN為數(shù)據(jù)信號(hào)屏蔽位在突發(fā)寫傳輸時(shí)屏蔽不存儲(chǔ)的數(shù)

據(jù);RAS/CAS/WE作為命令信號(hào)線向DDR2發(fā)出讀取、寫人、刷新或預(yù)充電命令;片內(nèi)終結(jié)信號(hào)線ODT控制是否需要DDR2進(jìn)行片內(nèi)終結(jié)。

3 DDR2控制器的設(shè)計(jì)原理

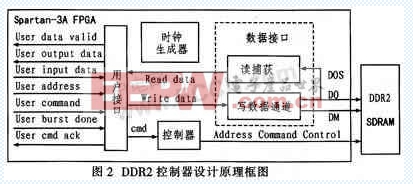

基于FPGA的DDR2控制器設(shè)計(jì)是由時(shí)鐘生成模塊、存儲(chǔ)控制模塊和讀寫數(shù)據(jù)接口模塊組成如圖2所示。

控 制器中所有模塊時(shí)鐘均來(lái)自于時(shí)鐘生成模塊,它由數(shù)字時(shí)鐘管理器(DCM)控制,輸出90°、180°和270°時(shí)鐘。該模塊還包含延遲校準(zhǔn)監(jiān)視器,用于校 準(zhǔn)讀取數(shù)據(jù)(DQ)對(duì)讀取數(shù)據(jù)選通脈沖(DQS)的延遲,以便讀取數(shù)據(jù)選通脈沖邊沿能夠正確對(duì)齊DQ有效窗口的中間位置。

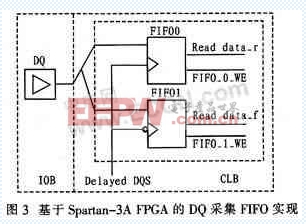

讀 寫數(shù)據(jù)接口模 塊是整個(gè)控制器設(shè)計(jì)的關(guān)鍵,它負(fù)責(zé)將用戶寫入的數(shù)據(jù)DQ和DOS按照DDR2SDRAM時(shí)序要求發(fā)送給DDR2,DDR2在DQS的每一個(gè)時(shí)鐘沿采集寫數(shù) 據(jù)。在讀取數(shù)據(jù)時(shí),DDR2SDRAM將DQS和相關(guān)數(shù)據(jù)發(fā)送到與DQ對(duì)齊邊沿的FPGA。FPGA將接收到的DQS信號(hào)經(jīng)過(guò)延遲校準(zhǔn),作為內(nèi)部存儲(chǔ)讀數(shù) 據(jù)的FIFO的寫時(shí)鐘。FPGA為DDR2的每個(gè)數(shù)據(jù)位配置一對(duì)讀寫異步的FIFO,每個(gè)數(shù)據(jù)位都輸入到上升沿(FIFO0)和下降沿(FIFO1)的 FIFO中,實(shí)現(xiàn)原理如圖3所示。

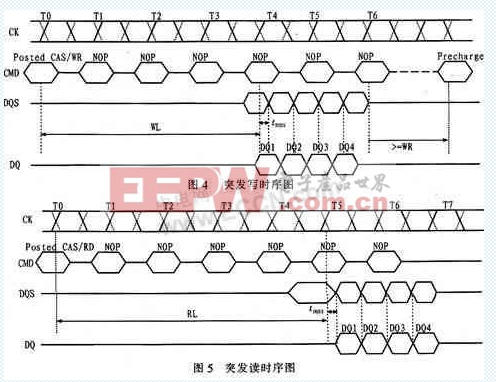

存 儲(chǔ)控制模塊用于產(chǎn)生DDR2所需的地址和命令信號(hào)。DDR2在正常的讀寫操作前要初始化,因此需向DDR2發(fā)送初始化命令,待初始化完成后才能發(fā)送讀寫命 令。對(duì)DDR2SDRAM的讀寫訪問(wèn)為突發(fā)模式。突發(fā)寫操作需向DDR2提供寫命令(User_command)、寫數(shù)據(jù) (User_input_data)和寫地址(User_address)信號(hào),在最后一個(gè)寫地址發(fā)送突發(fā)操作完成信號(hào) (User_burst_done),并保持2個(gè)時(shí)鐘周期有效下終止寫操作,突發(fā)寫時(shí)序如圖4所示。突發(fā)讀操作需向DDR2提供讀命令 (User_comm-and)和讀地址(User-address),在最后一讀地址發(fā)送突發(fā)完成信號(hào)(User-burst_done),并保持2個(gè) 周期有效下終止讀操作,突發(fā)讀時(shí)序如圖5所示

4 DDR2控制器的設(shè)計(jì)及應(yīng)用

為

了縮短開(kāi)發(fā)周期,采用Xilinx的MIG軟件工具直接生成DDR2控制器設(shè)計(jì)模塊,包括HDL代碼和約束文件。用戶可在MIG的GUI圖形界面選擇對(duì)應(yīng)

模板、總線寬度和速度級(jí)別,并設(shè)置CAS延遲、突發(fā)長(zhǎng)度、引腳分配等關(guān)鍵參數(shù)。如果設(shè)計(jì)者所選器件與MIG所列模板不相符,可在代碼生成后靈活修改代碼,

達(dá)到系統(tǒng)要求。代碼添加到工程前需硬件驗(yàn)證,采用MIG自動(dòng)生成的測(cè)試模塊進(jìn)行驗(yàn)證。該模塊向存儲(chǔ)器發(fā)出一系列的寫入命令和讀取命令,并對(duì)寫入數(shù)據(jù)和讀回

數(shù)據(jù)進(jìn)行比較,通過(guò)比較信號(hào)(led_error)驗(yàn)證控制器的正確與否。用ChipScope抓取的讀數(shù)據(jù)和相關(guān)控制信號(hào)時(shí)序分別如圖6和圖7所示,讀 寫比較信號(hào)(led_error)在檢測(cè)到讀寫數(shù)據(jù)相等時(shí)輸出'0'電平。

在 硬件驗(yàn)證通過(guò)后,把控制器代碼導(dǎo)入到系統(tǒng)工程中,設(shè)計(jì)者只需輸 入相應(yīng)命令(包括讀、寫和初始化命令),控制器模塊將自動(dòng)產(chǎn)生命令和控制信號(hào)并按照DDR2的時(shí)序要求送至DDR2,命令發(fā)送完畢提供給用戶一個(gè)命令應(yīng)答 信號(hào)(User_cmd_ack),設(shè)計(jì)者根據(jù)這一信號(hào)判斷是否可以發(fā)送下一個(gè)命令。至于自動(dòng)刷新、激活和預(yù)充電命令則由控制器自動(dòng)完成,無(wú)需用戶干涉。

===========================================

深圳市毅創(chuàng)騰電子科技有限公司

電話:(86)-755-83210909 83616256 83210801 83213361

企業(yè)QQ: 2355507165 / 2355507163

網(wǎng)址:m.jnmzyz.com

===========================================

深圳市毅創(chuàng)騰電子科技有限公司是一家大型、專業(yè)的XILINX(賽靈思)、ALTERA(阿特拉)、FREESCALE(飛思卡爾)、Analog Devices、TexasInstruments嵌入式FPGA、CPLD、微控制器、數(shù)字信號(hào)處理等集成電路銷售與服務(wù)的授權(quán)分銷商。也是亞太地區(qū)最大規(guī)模的原裝XILINX、ALTERA、FREESCALE產(chǎn)品供應(yīng)商之一。

===========================================

| EN25QH64-104HIP |

| EP1C3T100I7N |

| EP1C6Q240C8N |

| EP1C6Q240I7N |

| EP2AGX260FF35I3N |

| EP2AGX45DF25I3N |

| EP2AGX65DF29I3N |

| EP2AGX95EF29I5N |

| EP2C35F484C6N |

| EP2C35F484I8N |

| EP2C35F672C8N |

| EP2C50F484I8N |

| EP2C5F256I8N |

| EP2C5Q208C6N |

| EP2C5T144C8N |

| EP2C70F672I8N |

| EP2C70F896I8N |

| EP2C8Q208I8 |

| EP2C8Q208I8N |

| EP2S130F1020I4N |

| EP2S180F1020I4N |

| EP2S60F484I4N |

| EP2S90F1020C4N |

| EP2S90F1020I4N |

| EP2SGX90EF1152I4N |

| EP3C120F484I7N |

| EP3C120F780C7N |

| EP3C120F780C8N |

| EP3C120F780I7N |

| EP3C16F484C8N |

| EP3C25F256I7N |

| EP3C40F324C8N |

| EP3C40F484C8N |

| EP3C40F484I7N |

| EP3C55F780I7N |

| EP3C5E144I7N |

| EP3C5F256C8N |

| EP3C80F780C6N |

| EP3SL110F780C2N |

| EP4CE10E22C8N |

| EP4CE10F17C8N |

| EP4CE10F17I7N |

| EP4CE11529C8N |

| EP4CE115F23C8N |

| EP4CE115F29C8N |

| EP4CE15E22I7N |

| EP4CE15F17C6N |

| EP4CE15F17C8N |

| EP4CE22E22I7N |

| EP4CE22F17C7N |

| EP4CE40F29I7N |

| EP4CE422E22I7N |

| EP4CE55F23C8N |

| EP4CE6E22C8N |

| EP4CE6F17I8N |

| EP4CGX150DF27I7N |

| EP4CGX150DF31I7N |

| EP4CGX15BF14C8N |

| EP4CGX15DF27I7N |

| EP4CGX75CF23I7N |

| EP4SGX110DF29C4N |

| EP4SGX110HF35C2N |

| EP4SGX180KF40C2N |

| EP4SGX180KF40C3N |

| EP4SGX230FF35I4N |

| EP4SGX230KF40C2N |

| EP4SGX230KF40C3N |

| EP4SGX230KF40I4N |

| EPCQ256SI16N |

| EPCS128SI16N |

| EPCS16SI16N |

| EPCS16SI8N |

| EPCS4N |

| EPCS4SI8N |

| EPCS64SI16N |

| EPM2210F256C5N |

| EPM2210F324I5N |

| EPM240T100C5N |

| EPM240T100I5N |

| EPM3064ATC44-4N |

| EPM570T100I5N |

| EPM570T144I5 |

| EPM7064AETI44-7N |

| EPM7064STI44-6 |

| EPM7064STI44-7N |

| EPM7128STI100-10N |

| EPM9320ALI84-10 |

| EPM9320LI84-20 |

| FAN1112S |

| FDC6331L |

| FJV3109RMLF |

| FLM7179-18F |

| FM25V01-G |

| FOD3150 |

| FZT857 |

| G6K-2G-Y-5VDC |

| GAL20V8B-15LPI |

| HCPL-0631-500E |

| HMC1055CP23CE |

| HMC1055LPZCE |

| HMC546MS8G |

| HMC624CP4 |

| HMC624LP4 |

| HSP50415VI |

| HT1621D |

| HX0068ANL |

| HX5004NL |

| IDT7052L25PFI |

| IN4002 |

| IN4148 |

| IP175G |